Verilog 1장 - 4bit RCA

2019. 9. 19. 00:42ㆍProgramming/Verilog

Verilog를 공부하는 과정에 배운것을 정리한 것으로 틀린부분이 있을 수 있음을 알립니다.

RCA란?

RCA(Ripple Carry Adder)의 줄임말로 컴퓨터에서 사용되는 가산기의 종류 중 하나이다. 들어온 Carry-in이 물결처럼(Ripple) 진행되어 Carry-out으로 출력된다고 하여 붙여진 이름

RCA의 구성요소

4-bit RCA는 Full Adder 4개를 직렬로 연결한 것으로 첫번째 Full Adder가 Carry-in을 받고 Carry-out을 그다음 Full Adder로 넘겨주게 되며 마지막 Full Adder가 최종 Carry-out을 출력하게 된다.

Verilog Code

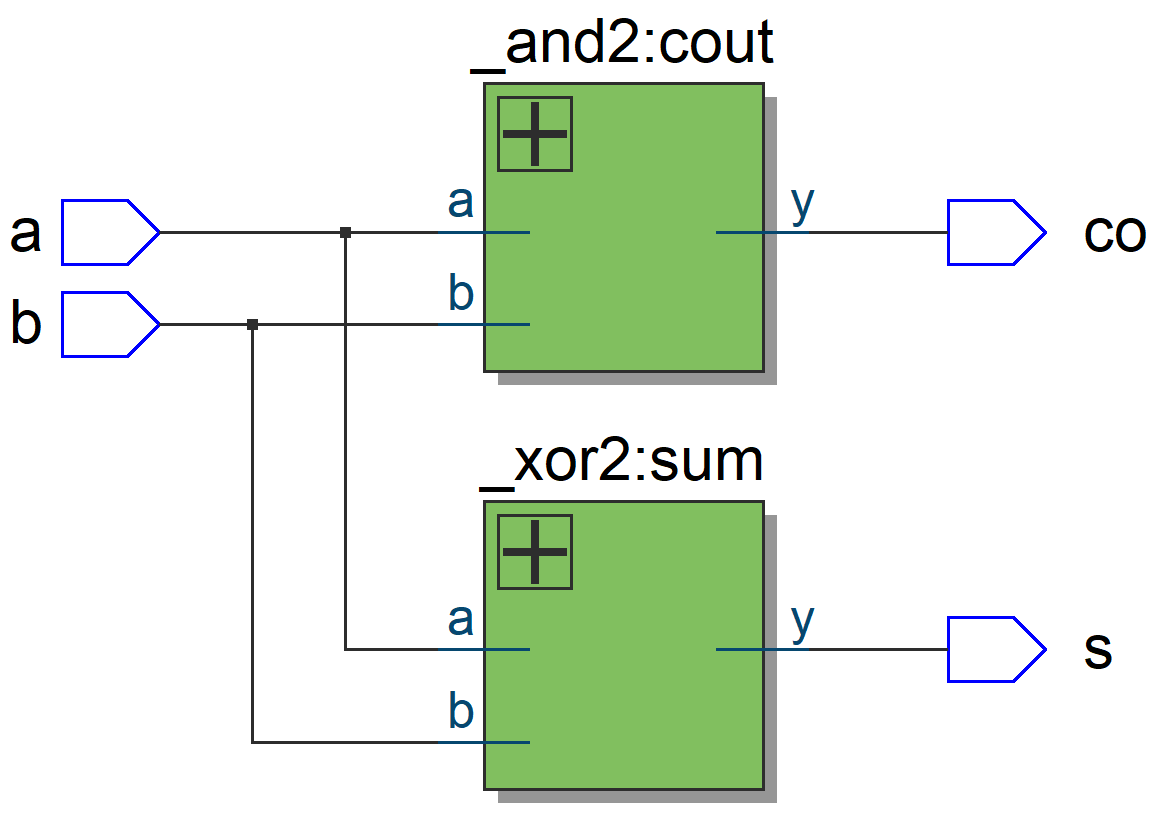

Half Adder

module ha(a, b, s, co);

input a, b;

output s, co;

// get sum from xor gate

_xor2 sum(a, b, s);

// get carry out from and gate

_and2 cout(a, b, co);

endmodule

Full Adder

module fa(input a, b, ci, output s, co);

// input a, b, ci and output s and co

wire c1, c2, sm;

// get sum from Half Adder

ha _ha1(.a(b), .b(ci), .s(sm), .co(c1));

ha _ha2(.a(a), .b(sm), .s(s), .co(c2));

// get carry out from OR gate

_or2 or1(.a(c2), .b(c1), .y(co));

endmodule

RCA

module rca(a, b, ci, s, co);

input [3:0] a, b;

input ci;

output [3:0] s;

output co;

wire [2:0] c;

// connect Full Adder

// connect to next Full Adder

fa U0_fa(.a(a[0]), .b(b[0]), .ci(ci), .s(s[0]), .co(c[0]));

// connect to next Full Adder

fa U1_fa(.a(a[1]), .b(b[1]), .ci(c[0]), .s(s[1]), .co(c[1]));

// connect to next Full Adder

fa U2_fa(.a(a[2]), .b(b[2]), .ci(c[1]), .s(s[2]), .co(c[2]));

// carry out

fa U3_fa(.a(a[3]), .b(b[3]), .ci(c[2]), .s(s[3]), .co(co));

endmodule

'Programming > Verilog' 카테고리의 다른 글

| Verilog 2장 - CLA (0) | 2019.12.15 |

|---|